El estándar ECSS-Q-ST-70-38C define de forma precisa los requisitos técnicos y las provisiones de garantía de calidad para la fabricación y la verificación de los circuitos electrónicos de alta fiabilidad basados en el dispositivo montado en la superficie (SMD) y la tecnología mixta.

Además, se definen las herramientas adecuadas, los materiales correctos, el diseño y las habilidades requeridos para discernir entre un trabajo adecuado y uno inadecuado.

Sin embargo, la preparación de las muestras que se deben inspeccionar es un trabajo complicado.

Inspecciones microseccionales

Se realizan inspecciones mediante microsección como parte del programa de verificación definido en el estándar ECSS-Q-ST-70-38C. Este ensayo implica el examen de las conexiones por soldadura de los distintos dispositivos electrónicos compuestos por diferentes materiales cuyas propiedades responden de formas totalmente distintas al método de seccionado usado. Esto implica adaptar los parámetros de pulido y esmerilado en función de cada caso. Para determinar la relación entre estos parámetros y la calidad del área inspeccionada, el diseño de los experimentos (DOE) ha sido una herramienta decisiva. Esta metodología ha permitido identificar las principales variables del proceso de seccionado para predecir los resultados finales y garantizar la replicabilidad.

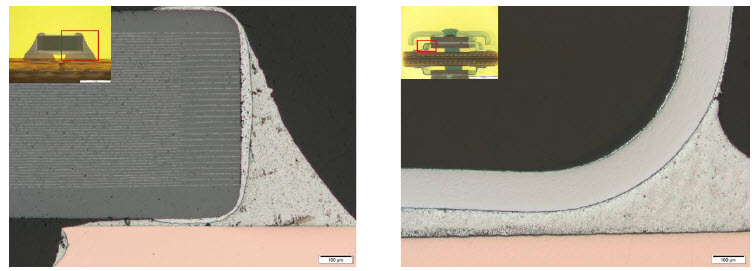

Este debate se centrará en la evaluación de distintos procesos de esmerilado en función de los resultados obtenidos con la metodología DOE. Como el proceso de seccionado depende principalmente de la dureza y ductilidad de los materiales que se deben esmerilar, los componentes electrónicos se agruparon según su composición. Para cada una de estas familias, se evaluaron los parámetros de esmerilado (tiempo, presión y velocidad de rotación) y los materiales abrasivos. De esta forma, se halló el proceso óptimo para cada dispositivo, tal y como se muestra en la figura 1.

El uso de la metodología DOE ha permitido reducir el tiempo y los recursos empleados para obtener el método de seccionado para cada dispositivo electrónico. Además, esta estrategia se puede implementar para identificar el proceso óptimo para cada componente antes de someterlo a un ensayo destructivo.

Evaluación de las técnicas de microsección para análisis materialográficos de dispositivos electrónicos

Figura 1. Área microseccionada de un capacitador cerámico y un componente FP usando dos métodos de esmerilado diferentes. Izquierda: Proceso de esmerilado con papeles SiC. Derecha: Proceso de esmerilado con superficies revestidas con partículas de diamante.

Autores: Carmen López-López, Sonia Reina, Manuel Domínguez, David Núñez Teruel.