Determinación de la Dureza de la Radiación de las Estructuras SIC MOS

Centro Nacional de Microelectrónica (CNM) Instituto de Microelectrónica de Barcelona (IMB), Barcelona (España)

Motivación y Estrategia de Estudio

El objetivo de este estudio es apoyar el desarrollo de un MOSFET europeo discreto de potencia de SiC endurecido a la radiación para su uso en aplicaciones espaciales mediante el estudio del óxido de puerta en términos de SEE y TID como uno de los parámetros clave en el futuro desarrollo de estos dispositivos. También se estudió la resistencia de las uniones P/N presentes en estos dispositivos teniendo en cuenta los problemas observados en las uniones de Schottky bajo radiación de iones pesados combinados con alta tensión.

Se siguió el siguiente enfoque para comprender mejor la sensibilidad de SiC Power MOSFET:

- Estudio del proceso de oxidación del óxido de la puerta y de la geometría de la puerta: 3 procesos de oxidación + 5 geometrías de compuerta probadas bajo iones gamma y pesados

- Prueba de iones pesados de 600V HV L-DMOS con óxido de puerta dopado con boro experimental que podría mejorar la dureza de la radiación.

- Iones pesados en diodos PIN de 1200V totalmente representativos de los que están incorporados en los MOSFETs de potencia.

Procesos de Oxidación de Compuertas y Geometrías

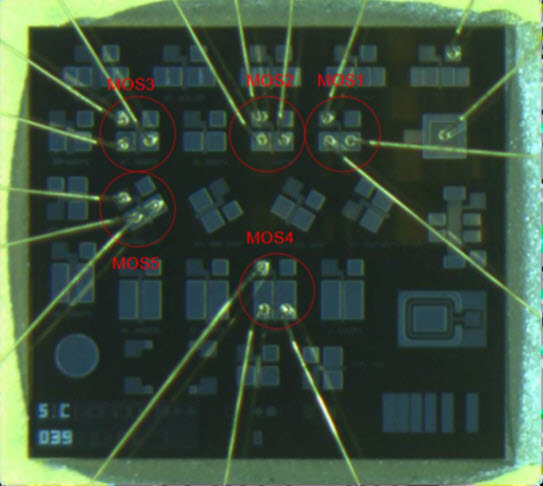

Descripción de los DUTs: SiC Lateral MOS

Ox1: Óxido de SiO2 delgado de puerta de crecimiento térmico en ambiente N2O + deposición de TEOS 400 Å

Ox2: Óxido de SiO2 + dopado con Boro 1 + TEOS 400 Å

Ox3: Óxido de SiO2 delgado de puerta de crecimiento térmico en ambiente de N2O + deposición de TEOS 400 Å con optimización del proceso de oxidación

Resultados:

- No hay fallas bajo haces de iones pesados de hasta LET=62.5MeV /mg/cm2

- Recuperación total después del recocido para gamma (300Krad)

- Pequeñas diferencias entre los tipos de óxidos y ninguna diferencia entre las geometrías de las compuertas

Gate Oxidation Results

| wdt_ID | DUT | Gate Width (μm) | Gate Length (μm) | Channel Rotation Vs flat (11-20) (°) |

|---|---|---|---|---|

| 1 | MOS1 | 2 | 150 | 0 |

| 2 | MOS2 | 4 | 150 | 0 |

| 3 | MOS3 | 24 | 150 | 0 |

| 4 | MOS4 | 4 | 300 | 0 |

| 5 | MOS5 | 24 | 150 | 30 |

| DUT | Gate Width (μm) | Gate Length (μm) | Channel Rotation Vs flat (11-20) (°) |

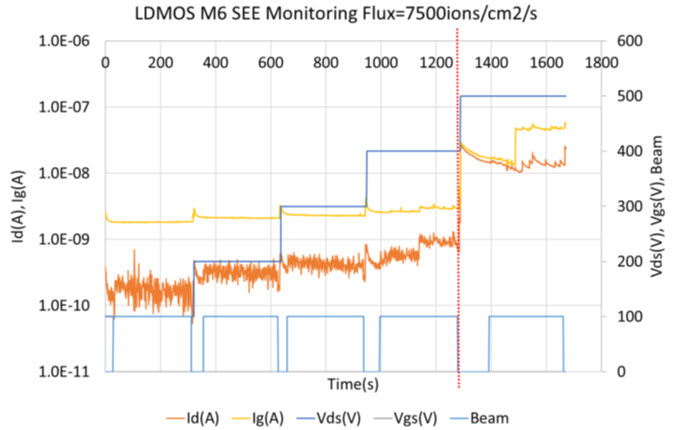

HV L-DMOS Bajo Iones Pesados

Daños catastróficos de los dispositivos para valores de sesgo tan bajos como VDS=200V para valores LET de 32.4 y VDS=400V para 20.4 MeV/cm2/mg(Si). El daño se produce durante la radiación durante la polarización o durante los PIGS intermedios después de un paso.

Resultados:

| wdt_ID | LET | VGS (V) | VDS (V) | Damage |

|---|---|---|---|---|

| 1 | 10.0 | 0, 2.5, -5 | 0 | no |

| 2 | 20.4 | 0, 2.5, -5 | 0 | no |

| 3 | 32.4 | 0, 2.5, -5 | 0 | no |

| 4 | 10.0 | 0 | up to 500 | no |

| 5 | 20.4 | 0 | up to 500 | PIGS after 400V run |

| 6 | 32.4 | 0 | up to 500 | PIGS after 200V run |

| 7 | 62.5 | 0 | up to 500 | 200V run |

| 8 | 20.4 | -5 | up to 500 | 400V run |

| 9 | ||||

| LET | VGS (V) | VDS (V) | Damage |

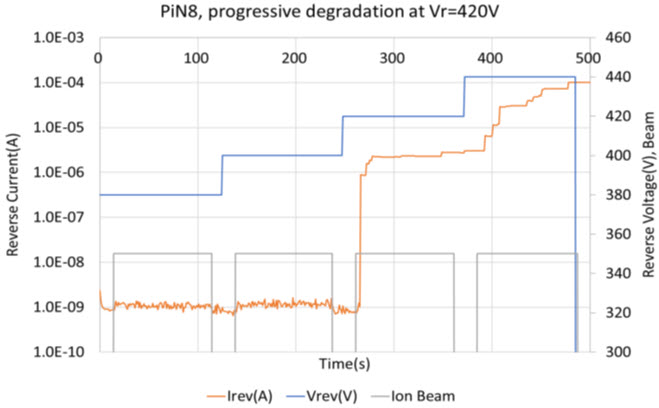

Diodos PIN Bajo Iones Pesados

Los diodos incorporados probados por separado revelaron la sensibilidad de esta área del MOSFET de potencia a iones pesados mientras se aplica HV. El daño del PIN ocurre para voltajes inversos ligeramente más altos que para Schottky de estudios previos.

Resultados:

| wdt_ID | DUT | LET | Vrev Step (V) | Failure at |

|---|---|---|---|---|

| 1 | PiN1 | 10.0 | 100 | abrupt failure @500V |

| 2 | PiN2 | 20.4 | 100 | abrupt failure @500V |

| 3 | PiN3 | 32.4 | 100 | degradation @400V |

| 4 | PiN4 | 62.5 | 100 | degradation @400V |

| 5 | PiN7 | 20.4 | 25 | degradation @400V |

| 6 | PiN8 | 20.4 | 20 | degradation @420V |

| 7 | PiN9 | 32.4 | 25 | degradation @400V |

| 8 | PiN11 | 32.4 | 20 | degradation @400V |

| DUT | LET | Vrev Step (V) | Failure at |

Conclusión

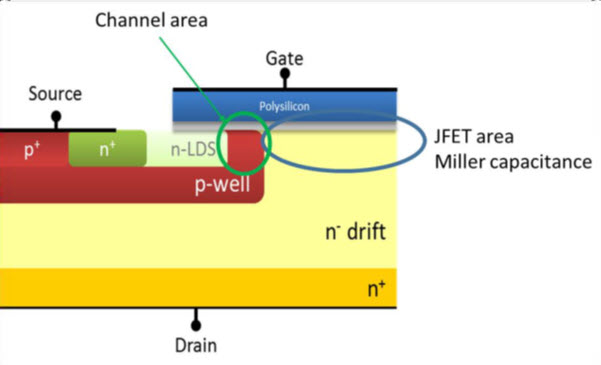

– La prueba de SEE del MOS lateral no reveló sensibilidad de los dispositivos a los iones pesados. Una posible explicación para esto podría ser que el daño en el DMOS vertical se localiza principalmente en el área JFET entre los pozos que están sometidos a campos eléctricos más altos. No se detectaron diferencias importantes entre los procesos de oxidación y las geometrías de las compuertas. Sin embargo, se observó un comportamiento ligeramente mejor bajo radiación gamma en los dispositivos con dispositivos dopados con boro.

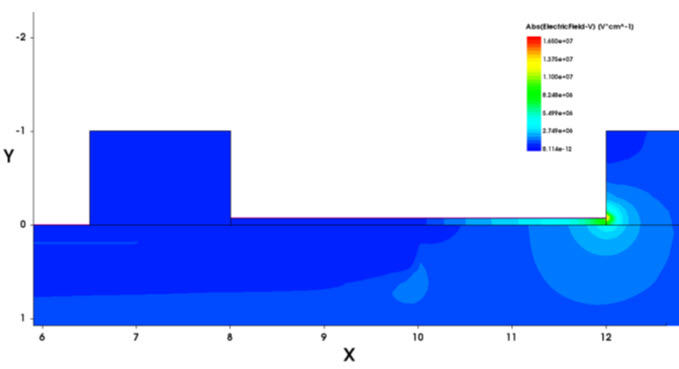

– La prueba de SEE del L-DMOS: En los dispositivos de potencia verticales, el área débil es la zona JFET situada debajo de la compuerta entre los pozos. En el LDMOS, no hay área JFET ya que la celda superior no es simétrica. En estas estructuras, el pico alto del campo eléctrico suele estar al final de la metalización de la puerta, donde probablemente se encontraba el punto de ruptura durante nuestra campaña. Mientras que en los MOSFETs de potencia vertical, la avería se produce en el bulto, ya sea en la unión del pozo P o en la unión de terminación.

La modelización de la distribución del campo eléctrico en el LDMOS a 500V muestra claramente el campo eléctrico máximo situado en el extremo de la puerta metálica. Una clara mejora  de este dispositivo podría ser entonces aumentar el óxido por debajo del metal en el extremo de la puerta. Para el L-DMOS bajo prueba, el daño se localiza en un área diferente que en el DMOS vertical. Esto explica la degradación que ocurre durante los pasos de irradiación, mientras que en una estructura vertical, el daño es usualmente revelado durante los PIGS.

de este dispositivo podría ser entonces aumentar el óxido por debajo del metal en el extremo de la puerta. Para el L-DMOS bajo prueba, el daño se localiza en un área diferente que en el DMOS vertical. Esto explica la degradación que ocurre durante los pasos de irradiación, mientras que en una estructura vertical, el daño es usualmente revelado durante los PIGS.

-Las pruebas de los diodos PIN de 1200V revelaron sensibilidad a los iones pero mejor comportamiento que los diodos Schottky de 1200V. La dependencia del daño con LET también es menor para los diodos PIN. El análisis  a termográfico de los dispositivos dañados muestra diferentes modos de falla para diferentes dispositivos, observando tanto el daño uniforme en el área de unión como los puntos calientes locales probablemente ubicados en puntos ya defectuosos del cristal, dependiendo de la muestra analizada.

a termográfico de los dispositivos dañados muestra diferentes modos de falla para diferentes dispositivos, observando tanto el daño uniforme en el área de unión como los puntos calientes locales probablemente ubicados en puntos ya defectuosos del cristal, dependiendo de la muestra analizada.

Agradecimientos

Project funded by European Space Agency, AO/1-8081/14/NL/KML “Prototyping and Characterization of Radiation Hardened SiC MOS Structures”

- Inmunidad conducida - 20th mayo 2019

- Ensayos de Transitorios eléctricos - 2nd mayo 2019

- Ensayo Campo de RF radiado - 2nd mayo 2019