Talk summary:

Third party dice radiation test for a manufacturer has never been an easy thing thanks to the exigent requirement from the users and difficulties from the die side. Things are becoming worse since the semiconductor came into a sub-micron and deep sub-micron era. New challenges and 3D PLUS radiation test strategies are presented.

The General background is that the space market volume is negligible comparing to commercial market – no bargaining power.

What ever RH die or COTs, the detail designs are always treated as confidential by semiconductor – mostly cases are like the black box; Sometimes it is difficult to get general process information (ex: bipolar? CMOS? bulk? epi?…), and most time it is impossible to get detail process information (ex: gate oxide, isolation structure details…) – hard to estimate the radiation characteristics.

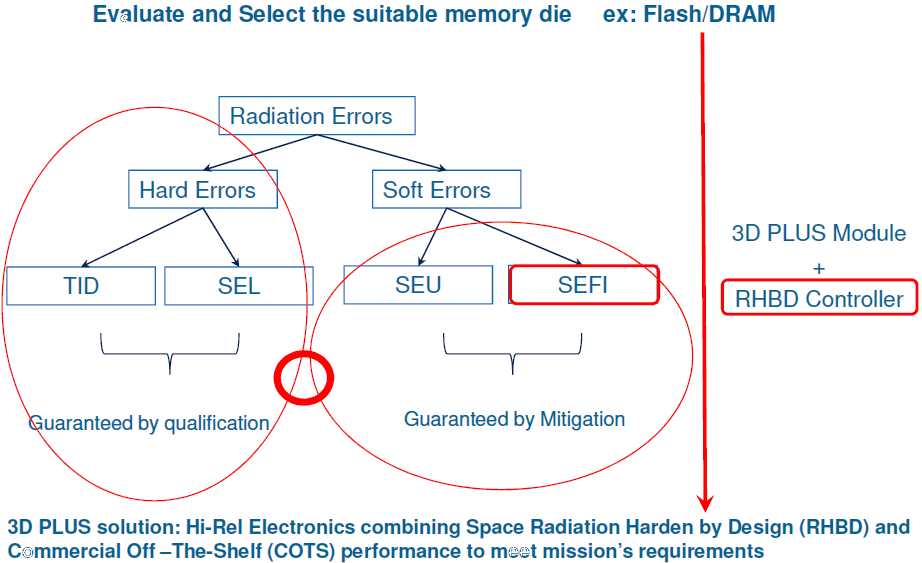

Radiation test strategies for a manufacturer

Radiation test strategies for a manufacturer using third party dice

When the space comes into high scaling Deep submicron (DSM) semiconductors, new technical & commercial challenges show up:

⇒Technically, DSM radiation behavior is complicated to manage:

- New structure & process are not always good to radiation;

- Big variations from process to process, manufacturer to manufacturer, design to design, revision to revision, P/N to P/N, lot to lot and even now piece to piece;

- Hard error mix with soft error: bit flip from TID; Micro Latch up (High current SEFI) & SEL, permanent SEFI

- Complicated Soft errors: single bit error, double bit error, multi-bit error, row error, column error, stuck bit, persistent flip bit & annealing, temporary SEFI, persistent SEFI, device SEFI, high current event…

⇒Commercially, Semiconductors optimize their manufacturing to lower the cost, but it is sometimes

catastrophe to space:

- Shrinking the process, modifying the materials, changing the foundry

- Shorter life cycle: 6 months to 1 year life cycle comparing 1 to 2 years component qualification

- Semiconductor Product Long Life Management (PLM) is highly risky to space traceability

- Combining Die design makes die mask verification difficult (MLC & SLC)

The new radiation test challenge and 3D PLUS solution

- A fairly large evaluations when looking for the candidate (ex: around 20 SRAMs had been scanned)

- Make the completely qualification (following ECSS/ESCC standard) when a potential good die shows up

- Make a strategic inventory (bargaining power) at 3D PLUS to make sure traceability and technical supports

- Reuse the result and do further design oriented tests to put more added values

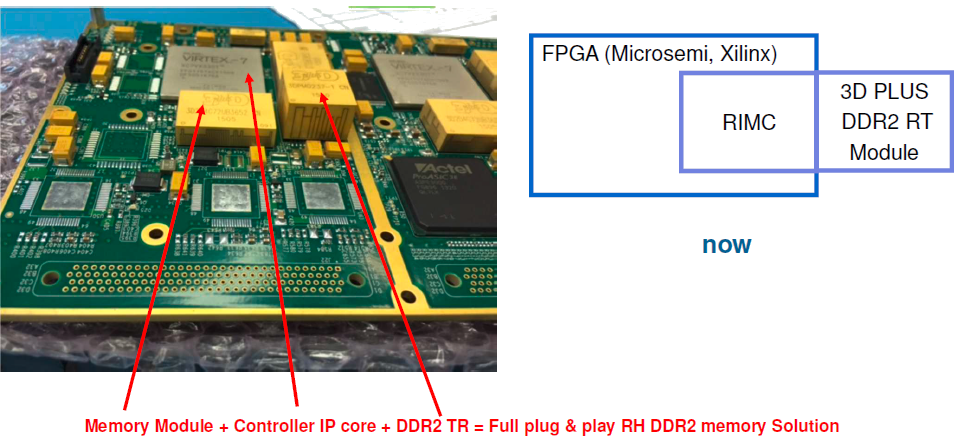

RIMC IP – RH DDR2/3 Solution

3D PLUS radiation test strategies to use third party dice:

- Following ECSS/ESCC standard to do the radiation test

- Maintain a privilage relationship with semiconductors

- More added value tests oriented to design (radiation mitigation)

Download or read the full report here

- Quantum Key Distribution - 7th November 2022

- Conducted Immunity - 20th May 2019

- Electrical transients Test - 2nd May 2019