Talk summary:

VA160 and VATA160 are used as front-end readout ASICs in the payloads of DAMPE. Both Laser pulse test and heavy ion beam test were conducted to get the SEL tolerance of the ASICs.

Laser test was performed firstly to quality the SEL sensitivity because it is easy and ready at all times. Heavy ion beam teat was executed secondly to quantify the SEL tolerance of the ASICs.

Test results shows that there is about 0.4 SEL event a year for one chip and about 3 events a mouth for the system. Current limitation circuit was designed to mitigate the SEL damage and was validated in Laser pulse test.

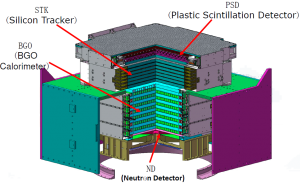

DAMPE

(Dark Matter Particle Explorer)

Supported by the Strategic Priority Programs on Space Science, Chinese Academy of Sciences

- Lunched on December 17th, 2015

- Mission period : > 3 years

- 500Km orbit

- DAMPE payloads:

– Plastic Scintillation Detector (PSD)

– Silicon Tracking (STK)

– BGO Calorimeter (BGO)

– Neutron Detector (ND)

The DAMPE Detector

Radiation Test to study the radiation tolerance – ASIC for DAMPE Mission

Front-End Readout ASICs

- VA160 and VATA160 for BGO Calorimeter

– 52 VA160 chips, 32 VATA160 chips - VA160 for Plastic Scintillation Detector

– 16 VA160 chips - VA140 for Silicon Tracker

– 1152 VA140 chips - Designed by IDEAS in Norway

– Based on VA32 and TA32, modified in I/O interface

– Fabricated by AMS in Austria, 0.35 CMOS process. - VA32: 32-channel read out in parallel/serial

- TA32: 32-channel trigger

- VATA=VA+TA

Radiation tolerance of the ASICs

Radiation: TID SEU SEL

- TID: long time effect and can be shielded, test data is needed for shielding, test can be performed at any time at low cost.

- SEU: instant effect and can be corrected using software, test data is not strongly demanded.

- SEL: instant effect and hard damage, test date is needed for mitigation, test is expensive and not always available.

SEU

Main part of VA160, VATA160and VA140 is analog circuit, which is not sensitive to SEU

VA: SEU risk mainly exists in the (32+32) shift registers:

- Reset the shift registers after every trigger, which greatly reduce the SEU probability, and the errors will not be accumulated.

TA: SEU risk mainly exists in the 165 bit configuration registers:

- TMR design is built in, the registers can detect SEU errors and correct them automatically, which greatly reduce the risk.

TID

TID test using 60Co source, in Beijing and USTC.

TID tests on VA32 and TA32:

- Total dose up to 25.2krad(Si).

- No notable change of performance after160 hour annealing@100℃.

TID tests for VA160 and VATA160:

Total dose up to 30 krad(Si)

TID tests for VA140

- Total dose up to 20 krad(Si)

From the TID results, the modification to VA32 does not change the TID tolerance a lot, so there maybe not much change in SEL.

SEL

More attentions were paid on SEL of ASICs:

- Hard error leading to permanent damage

- 68 VA160 chips, 32 VATA160 chips and 1152 VA140 chips used, there maybe lot of SEL events

- a series of SEL tests were conducted to evaluated the SEL tolerance.

SEL tests:

- using Laser pulse

- using ion beam

In orbit SEL events evaluation:

- Estimated SEL events of VA

- Estimated SEL events of VATA160(TA part)

Download or read the full report here

- Inmunidad conducida - 20th mayo 2019

- Ensayos de Transitorios eléctricos - 2nd mayo 2019

- Ensayo Campo de RF radiado - 2nd mayo 2019